LV010-I2S接口简介

一、I2S 简介

1. I2S 是什么?

I2S 全称 Inter-IC Sound, Integrated Interchip Sound,或简写 IIS,它是一种用于在数字音频设备之间传输音频数据的串行总线标准。是飞利浦(Philips)在 1986 年定义(1996 年修订),用于 解决在集成电路之间传输音频数据的问题,例如编解码器 CODEC、DSP、数字输入/输出接口、ADC、DAC 和数字滤波器等。除了都是由飞利浦定义外,I2S 和 I2C 没有任何关系。

这里有一些文档可以参考:I2S bus specification、pIYBAFy-2mqARQ7iAAGK2mjZDxg312.pdf

I2S 协议定义了音频数据的传输格式、时序和控制信号。在工作中音频采集和输出,AD 和主芯片之间的通信均是通过 I2S 进行通信的,其应用场景如下:

I2S RX 方向:麦克风在机械振动下将声音信号转变为电压信号,电压信号经过放大等处理,给到 ADC 采样,将模拟信号转化为数字信号;音频在 ADC 与 DSP 之间的传输协议就是使用的 I2S 协议。

I2S TX 方向:数字信号经过编码、存储、压缩等技术后,发送给解码器-DAC(DSP、专用解码器),将数字信号还原为模拟信号,最后给到喇叭完成声音/音频的播放。音频在 DAC 与 DSP 之间的传输就是使用 I2S 协议。

2. 系统通信配置框图

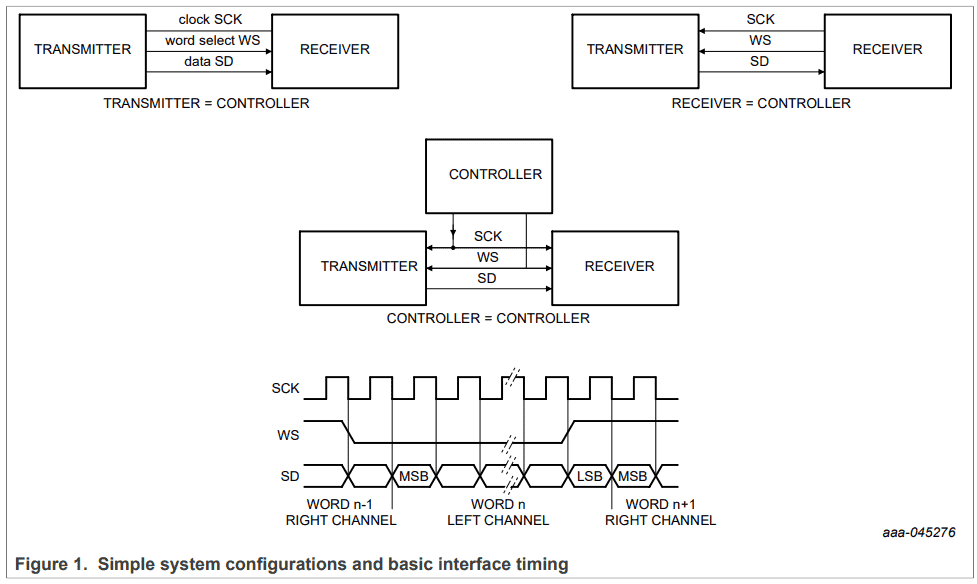

I2S bus specification 的 2 Basic serial bus requirements 部分有如下框图:

在 I2S 总线上,没有地址或设备选择机制,只能同时存在一个主设备和发送设备。主设备可以是发送设备,也可以是接收设备,或是协调发送设备和接收设备的其它控制设备。在 I2S 系统中,提供时钟(SCK 和 WS)的设备为主设备。

二、I2S 总线

1. 信号线

在 I2S 传输协议中,数据信号、时钟信号以及控制信号是分开传输的。I2S 协议只定义 三根 信号线:

- Continuous Serial Clock (SCK);

- Word Select (WS);

- Serial Data (SD);

产生 SCK 和 WS 的设备为控制器。

1.1 时钟信号 SCK

串行时钟 SCK(Continues Serial Clock),也叫位时钟(BCK)。不同厂家的芯片型号,时钟信号叫法可能不同,也可能称 BCLK/Bit Clock 或 SCL/Serial Clock。

每发送 1 位数字音频数据,SCK 上都有 1 个脉冲。SCK 的频率 = 2× 采样频率 × 采样位数。在数据传输过 程中,I2S 总线的发送器和接收器都可以作为系统的主机来提供系统的时钟频率。

SCK 是模块内的同步信号,从模式 时由外部提供,主模式 时由模块内部自己产生。

如何计算 SCK 频率?例如:设声音的 采样频率为 44.1 kHz,即声道选择信号(帧时钟)WS 的频率必须也为 44.1 kHz。左/右 2 个声道的量化深度均为 16 bit,则 I2S 的 SCK 的频率为:44.1 kHz × 16×2 =1.4112 MHz。

1.2 数据信号 SD

数据信号 SD(Serial Data) ,用于传输二进制补码表示的音频数据。

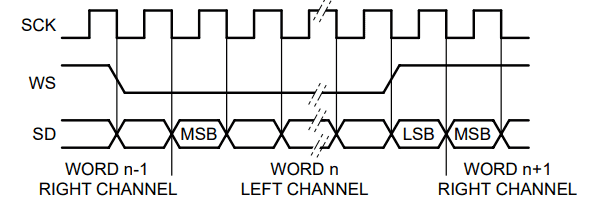

在 I2S 中以 二进制补码 的形式在数据线上传输。在 WS 变化后的第一个 SCK 脉冲,先传输最高位(MSB, Most Significant Bit)。先传送 MSB 是因为发送设备和接收设备的字长可能不同,当系统字长比数据发送端字长长的时候,数据传输就会出现截断的现象/Truncated,即如果数据接收端接收的数据位比它规定的字长长的话,那么规定字长最低位(LSB: Least Significant Bit)以后的所有位将会被忽略。如果接收的字长比它规定的字长短,那么空余出来的位将会以 0 填补。通过这种方式可以使音频信号的最高有效位得到传输,从而保证最好的听觉效果。

根据输入或输出特性,不同芯片上的 SD 也可能称 SDATA、SDIN、SDOUT、DACDAT、ADCDAT 等;数据发送既可以同步于 SCK 的上升沿,也可以是下降沿,但接收设备在 SCK 的上升沿采样,发送数据时序需考虑。

1.3 左右声道选择信号 WS

左右声道选择信号 WS(Word Select),也叫帧时钟 WS(有些地方也称为 LRCK/Left Right Clock),命令(声道)选择,用于切换左右声道的数据。WS 的频率等于采样频率,由系统主机提供。WS 为“1”表示传输的是左声道的 数据,WS 为“0”表示传输的是右声道的数据。

WS 既可以在 SCK 的上升沿,也可以在 SCK 的下降沿变化。从设备在 SCK 的上升沿采样 WS 信号。数据信号 MSB 在 WS 改变后的第二个时钟(SCK)上升沿有效(即延迟一个 SCK),这样可以让从设备有足够的时间以存储当前接收的数据,并准备好接收下一组数据。

1.4 MCLK

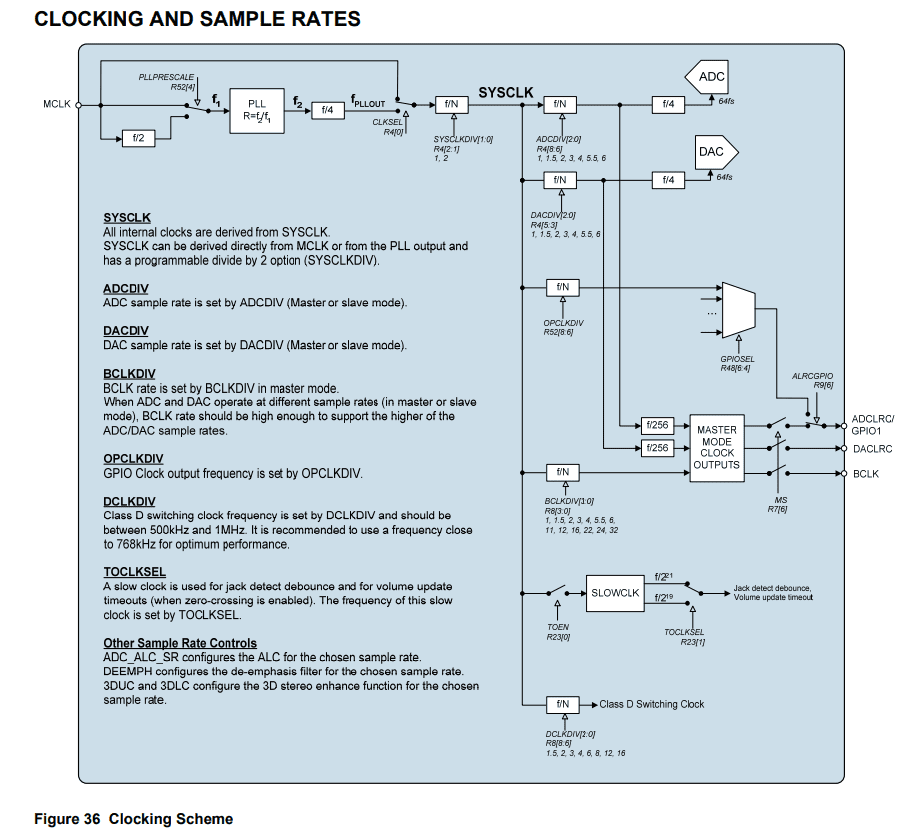

有时候为了使音频 CODEC 芯片与主控制器之间能够更好的同步,会引入另外一个叫做 MCLK(Master Clock) 的信号,也叫做主时钟或系统时钟,一般是采样率的 256 倍或 384 倍。

这是由 CODEC 内部基于 Delta-Sigma (ΔΣ)的架构设计要求使然。其主要原因是因为这类的 CODEC 没有所谓提供芯片的工作时钟晶振电路。它需要外部的时钟提供内部 PLL。如下图的 WM8960_DS 的时钟框图:

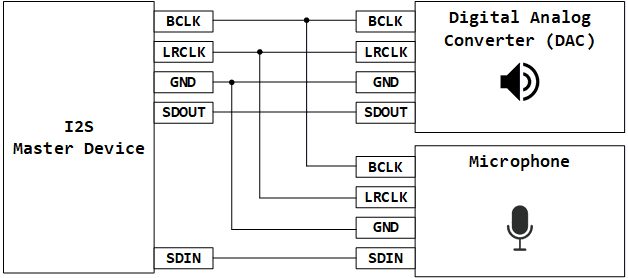

2. 硬件接口

3. 时序图

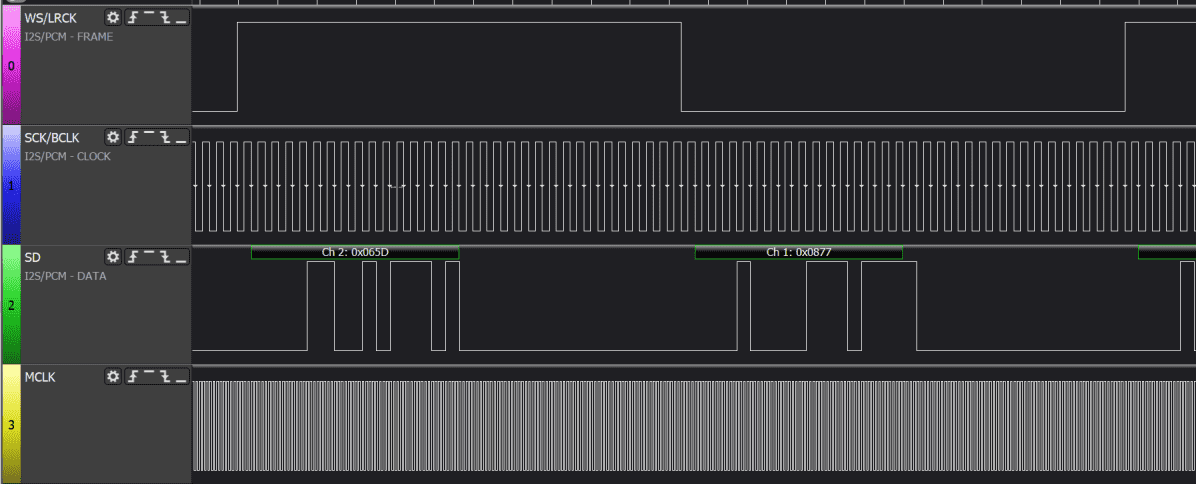

用逻辑分析仪抓取的真实的 I2S 时序图 如下:

通道 0 是 LRCK 时钟,通道 1 为 BCLK,通道 2 是 DACDATA,通道 3 是 MCLK。

4. 数据传输模式

I2S 接口标准中,存在三种数据传输模式,分别是:飞利浦标准模式(I2S mode),左对齐(Left Justified)和右对齐(Right Justified)三种传输模式。

这三种传输格式,基本都是相同的,不同之处在于 SD 数据同 WS 信号的对齐位置。左对齐的时候最高位数据在第一个时钟就出现,而右对齐的时候数据最低位在最后一个时钟出现,这就是他们的本质区别。

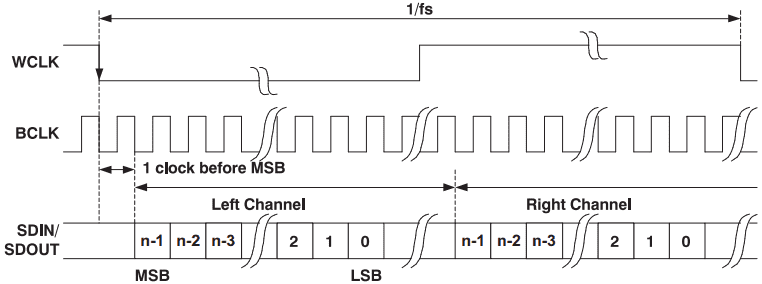

4.1 I2S mode

I2S 模式 属于左对齐中的一种特例,也叫 PHILIPS 模式,是由标准左对齐格式再 延迟一个时钟位(delay one clock)变化来的。时序如图 5 所示,左声道的数据 MSB 在 WS 下降沿之后第二个 SCK/BCLK 上升沿有效,右声道数据的 MSB 在 WS 上升沿之后第二个 SCK/BCLK 上升沿有效。

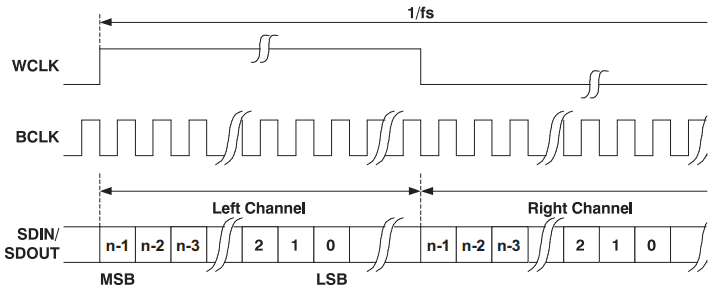

4.2 Left Justified

左对齐 较少使用,下图为左对齐时序图,和 PHILIPS 格式对比可以看出,标准左对齐格式的数据的 MSB 没有相对于 BCLK 延迟一个时钟。左对齐格式的左声道的数据 MSB 在 WS 上升沿之后 SCK/BCLK 的第一个上升沿有效;右声道的数据 MSB 在 WS 下降沿之后 SCK/BCLK 第一个上升沿有效。标准左对齐格式的优点在于,由于在 WS 变化后的第一个 SCK 上升沿就开始采样,它不需要关心左右声道数据的字长,只要 WS 的时钟周期足够长,左对齐的方式支持 16-32bit 字长格式。

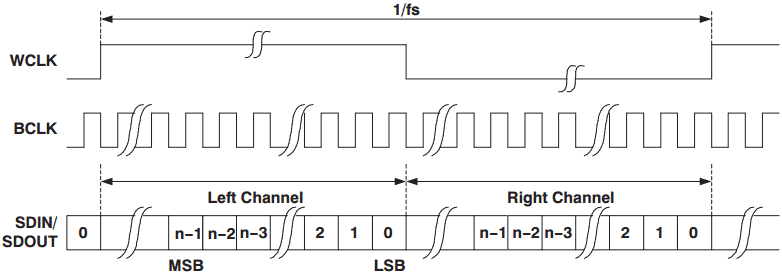

4.3 Right Justified

右对齐 也叫 EIAJ (Electronic Industries Association of Japan) 或 SONY 格式,图 7 为右对齐时序图。右对齐格式左声道的数据 LSB 在 WS 下降沿的前一个 SCK/BCLK 上升沿有效,右声道的数据 LSB 在 WS 上升沿的前一个 SCK/BCLK 上升沿有效。相比于标准左对齐格式,标准右对齐的不足在于接收设备必须事先知道待传数据的字长。这也解释了为什么许多 CODEC 都会提供多种右对齐格式选择功能。

参考资料:

数字音频接口(I2S, PCM/TDM, PDM)_pdm 接口-CSDN 博客